Product Summary

The 74HC74D is a dual positive edge triggered D-type flip-flop. The 74HC74D is a high-speed Si-gate CMOS device and is pin compatible with low power Schottky TTL (LSTTL). The 74HC74D is specified in compliance with JEDE standard no. 7A.

Parametrics

74HC74D absolute maximum ratings: (1)tPHL/tPLH propagation delay CL = 14 pF; VCC = 5 V nCP to nQ, nQ: 15 ns; (2)nSD to nQ, nQ: 15 ns; (3)nRD to nQ, nQ: 16 ns; (4)fmax maximum clock frequency: 76 MHz; (5)CI input capacitance: 3.5 pF; (6)CPD power dissipation capacitance per flip-flop notes 1 and 2: 24 pF; (7)Package temperature range: -40℃ to +125℃.

Features

74HC74D features: (1)Symmetrical output impedance; (2)Low power dissipation; (3)High noise immunity; (4)Balanced propagation delays; (5)Specified in compliance with JEDEC standard no. 7A.

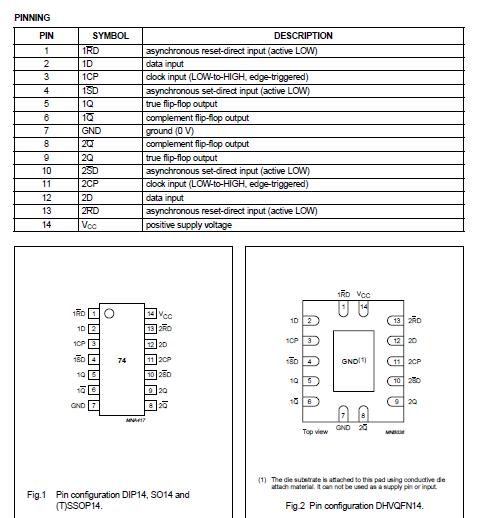

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC74D |

NXP Semiconductors |

Flip Flops DUAL D F/F POS-EDGE |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC74D,652 |

NXP Semiconductors |

Flip Flops DUAL D F/F POS-EDGE |

Data Sheet |

|

|

||||||||||||

|

74HC74D,653 |

NXP Semiconductors |

Flip Flops DUAL D-TYPE POSITIVE EDGE-TRIG |

Data Sheet |

|

|

||||||||||||

|

74HC74DB |

NXP Semiconductors |

Flip Flops DUAL D-TYPE POSITIVE EDGE-TRIG |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC74DB,112 |

NXP Semiconductors |

Flip Flops DUAL D-TYPE POSITIVE |

Data Sheet |

|

|

||||||||||||

|

74HC74DB,118 |

NXP Semiconductors |

Flip Flops DUAL D-TYPE POSITIVE |

Data Sheet |

|

|

||||||||||||

|

74HC74DB-T |

NXP Semiconductors |

Flip Flops DUAL D-TYPE POSITIVE EDGE-TRIG |

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC74DR2G |

ON Semiconductor |

Flip Flops DUAL D TYPE FLIP FLOP |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))